**July 2021**

Rev 1.0

**Abstract:** The standard is collateral-centric with a focus on security concerns; it applies to electrical designs that are integrated into other circuits. The standard defines a methodology that (1) identifies elements, such as input or output ports, that can influence the behavior of a critical section within the design and (2) associates known security weaknesses based on the type of design and/or critical section. The methodology uses data objects, which are both human and machine readable, to capture security relevant information through the architectural and design phase of the electrical design to be consumed by an Integrator for their product lifecycle. The standard is independent of existing standards and is not part of the electrical design itself.

**Keywords:** Security, RTL, attack surface, threat modeling, security weakness, mitigation, hardware, circuit design, integrated circuit, SoC, ASIC, IP

### **Notices**

Accellera Systems Initiative (Accellera) Standards documents are developed within Accellera and the Technical Committee of Accellera. Accellera develops its standards through a consensus development process, approved by its members and board of directors, which brings together volunteers representing varied viewpoints and interests to achieve the final product. Volunteers are members of Accellera and serve without compensation. While Accellera administers the process and establishes rules to promote fairness in the consensus development process, Accellera does not independently evaluate, test, or verify the accuracy of any of the information contained in its standards.

Use of an Accellera Standard is wholly voluntary. Accellera disclaims liability for any personal injury, property or other damage, of any nature whatsoever, whether special, indirect, consequential, or compensatory, directly or indirectly resulting from the publication, use of, or reliance upon this, or any other Accellera Standard document.

Accellera does not warrant or represent the accuracy or content of the material contained herein, and expressly disclaims any express or implied warranty, including any implied warranty of merchantability or suitability for a specific purpose, or that the use of the material contained herein is free from patent infringement. Accellera Standards documents are supplied "AS IS."

The existence of an Accellera Standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of an Accellera Standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change due to developments in the state of the art and comments received from users of the standard. Every Accellera Standard is subjected to review periodically for revision and update. Users are cautioned to check to determine that they have the latest edition of any Accellera Standard.

In publishing and making this document available, Accellera is not suggesting or rendering professional or other services for, or on behalf of, any person or entity. Nor is Accellera undertaking to perform any duty owed by any other person or entity to another. Any person utilizing this, and any other Accellera Standards document, should rely upon the advice of a competent professional in determining the exercise of reasonable care in any given circumstances.

Interpretations: Occasionally questions may arise regarding the meaning of portions of standards as they relate to specific applications. When the need for interpretations is brought to the attention of Accellera, Accellera will initiate action to prepare appropriate responses. Since Accellera Standards represent a consensus of concerned interests, it is important to ensure that any interpretation has also received the concurrence of a balance of interests. For this reason, Accellera and the members of its Technical Committees are not able to provide an instant response to interpretation requests except in those cases where the matter has previously received formal consideration.

Comments for revision of Accellera Standards are welcome from any interested party, regardless of membership affiliation with Accellera. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments. Comments on standards and requests for interpretations should be addressed to:

Accellera Systems Initiative 8698 Elk Grove Blvd Suite 1, #114 Elk Grove, CA 95624 USA

Note: Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken with

respect to the existence or validity of any patent rights in connection therewith. Accellera shall not be responsible for identifying patents for which a license may be required by an Accellera standard or for conducting inquiries into the legal validity or scope of those patents that are brought to its attention.

Accellera is the sole entity that may authorize the use of Accellera-owned certification marks and/or trademarks to indicate compliance with the materials set forth herein.

Authorization to photocopy portions of any individual standard for internal or personal use must be granted by Accellera, provided that permission is obtained from and any required fee is paid to Accellera. To arrange for authorization please contact Lynn Bannister, Accellera Systems Initiative, 8698 Elk Grove Blvd Suite 1, #114, Elk Grove, CA 95624, phone (916) 670-1056, e-mail lynn@accellera.org. Permission to photocopy portions of any individual standard for educational classroom use can also be obtained from Accellera. Suggestions for improvements to this standard are welcome and should be sent to the email reflector ipsa@lists.accellera.org.

# **Participants**

At the time this draft standard was completed, the Accellera IPSA Working Group had the following membership:

**Brent Sherman**, Intel Corp, *Chair* **Mike Borza**, Synopsys, *Vice Chair*

Sohrab Aftabjahani, Intel Corp. Adam Cron, Synopsys Monica Farkash, AMD Nicole Fern, Tortuga Logic Dave Graubart, Allied Member John Hallman, OneSpin Solutions Kathy Hayashi, Qualcomm, Inc. Nathan Mandelke, Cadence Design Systems, Inc. Jean-Philippe Martin, Intel Corp.

Steven McNeil, Xilinx, Inc.

Michael Munsey, Methodics,

Inc.

Anders Nordstrom, Tortuga

Logic

James Pangburn, Cadence

Design Systems, Inc.

Ambar Sarkar, NVIDIA Corp.

Yaron Schiller, Cadence Design Systems, Inc. Adam Sherer, Cadence Design Systems, Inc. Ireneusz Sobanski, Intel Corp. Badhri Uppiliappan, Analog Devices, Inc. Jesse Wyant, Intel Corp.

# Introduction

A System on Chip (SoC) or Application Specific Integrated Circuit (ASIC) is comprised of multiple components referred to as Intellectual Property (IP) blocks or just IP. These blocks come from multiple sources such as internal development teams, IP suppliers, tools to generate IP, etc. Typically, the SoC/ASIC owner integrates multiple IPs from multiple sources, which raises concerns about security risk. This standard addresses these concerns by introducing a methodology and formalized data objects that identify security risks an Integrator might inherit. These concerns may be addressed by an Integrator to make an informed decision at the time of IP integration. The options may be to select another IP with less risk, implement mitigations to address the concerns, or simply decide the risks are out of scope for the product.

The methodology uses two approaches to identify security concerns. One is to identify attack points that can be used to compromise the security of the IP block. These attack points are what an adversary would use to perform a malicious act on the design. By presenting this information, the Integrator can decide how to manage the associated risks. The other approach is to identify and associate known security concerns to an IP block. These concerns have been discovered, classified and published by fellow travelers in the industry, academia, or security researchers. Anyone researching security may be able to contribute to a knowledge base.

The standard is primarily directed towards IP developers and integrators. It is design, product, and tool independent. Users of this standard will be able to provide consistent security collateral in a uniform format.

# **Contents**

| Notices                                     | 3  |

|---------------------------------------------|----|

| 1. Overview                                 | 1  |

| 1.1 Scope                                   |    |

| 1.2 Purpose                                 |    |

| 1.3 Word usage                              |    |

| 2. Normative references                     |    |

|                                             |    |

| 3. Definitions, acronyms, and abbreviations |    |

| 3.1 Definitions                             |    |

| 3.2 Acronyms and abbreviations              | 3  |

| 4. Background                               | 5  |

| 5. SA-EDI Methodology                       | e  |

| 5.1 IP Bundle                               |    |

| 6. Security Weakness Knowledge Base         | 8  |

| 6.1 Format                                  |    |

| 6.2 Specifications                          |    |

| 7. Data Objects                             | 11 |

| 7.1 Data Object Language                    |    |

| 7.2 Asset Definition                        |    |

| 7.2.1 Specifications                        |    |

| 7.3 Database                                |    |

| 7.3.1 Specifications                        |    |

| 7.4 Element                                 |    |

| 7.4.1 Specifications                        |    |

| ±                                           |    |

| 7.5 Attack Points Security Objective (APSO) |    |

| 7.5.1 Specifications                        | 10 |

| 8. Threat Model                             | 17 |

| 9. Workflow Compliance                      | 17 |

| -                                           |    |

| Annex A : Data Object JSON Schema           | 19 |

| A.1 Asset Definition                        |    |

| A.2 Database                                |    |

| A.3 Element                                 |    |

| A.4 Attack Points Security Objective        |    |

| A.5 SA-EDI Data Object                      | 20 |

| Annex B : Use-case Example                  |    |

| B.1 Watchdog IP                             |    |

| B.1.1 Registers                             |    |

| B.2 Workflow Steps                          |    |

| B.2.1 WDIP Security Evaluation              | 29 |

| Annay C : WDID Sauraa Cada                  | 21 |

| C.1 wd_top.v     | 31 |

|------------------|----|

| C.2 wd_control.v | 32 |

| C.3 wd_count.v   |    |

|                  |    |

| Bibliography     | 36 |

### 1. Overview

The SA-EDI standard defines a specification that documents security concerns for hardware IP and its associated components when integrated into an Integrated Circuit. With the standard, IP Providers can identify security concerns to either: 1) mitigate in their IP; or 2) disclose to the Integrator to address at their level.

The standard is structured as follows: Section 4 introduces a background on the existing IP development process; Section 5 describes the proposed methodology to support the SA-EDI standard; Section 6 introduces the concept of a security weakness knowledge base which is comprised of known security concerns; Section 7 outlines the data objects in the standard; Section 8 is the threat model which is the end result; and Section 9 provides guidelines for compliance to the standard. The Annex sections provide additional information to help use the standard: Annex A outlines the JSON schema for the data objects; Annex B provides an example application to an IP; and Annex C contains the source code of the example IP.

The standard is completely contained in this document and any references to whitepapers such as [B1] are for background information only and are not considered part of the standard.

### 1.1 Scope

The standard defines data objects to identify critical elements in a digital hardware IP design and their associated security concerns. It defines the format and relationship of data objects that may be generated by tools during the hardware development process. Since the standard is external to the IP design, it can be applied to existing designs even if the hardware source (e.g., RTL) is encrypted.

The standard assumes the relationship between the IP Provider and Integrator is trusted. The standard does not address issues such as supplier credentialing; it simply provides a mechanism for an IP Provider to identify security concerns to an Integrator. Secure integration requires (among other things) that IP suppliers act in good faith by providing complete collateral.

### 1.2 Purpose

The intent of the standard is to identify known security concerns, documented in a knowledge base, associated with an asset and/or family type during IP integration. The IP Provider uses the standard to identify assets in the design that require a security objective (e.g., Confidentiality, Integrity, Availability)

and elements (e.g., ports, parameters, etc.) that can compromise the objective. The Integrator uses the collateral to create a threat model with identified mitigations to support the security objective. The methodology provides the means to validate security assurance collateral to an IP design.

1.3 Word usage

The word *shall* indicates mandatory requirements strictly to be followed in order to conform to the standard and from which no deviation is permitted (shall equals is required to).

The word *should* indicates that among several possibilities one is recommended as particularly suitable, without mentioning or excluding others; or that a certain course of action is preferred but not necessarily required (should equals is recommended that).

The word *may* is used to indicate a course of action permissible within the limits of the standard (may equals is permitted to).

The word *can* is used for statements of possibility and capability, whether material, physical, or causal (can equals is able to).

2. Normative references

The following referenced documents, if any are listed in this section, are indispensable for the application of this document (i.e., they must be understood and used, so each referenced document is cited in text and its relationship to this document is explained). For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments or corrigenda) applies.

3. Definitions, acronyms, and abbreviations

3.1 Definitions

For the purposes of this document, the following terms and definitions apply.

**Adversary**: A malicious entity that prevents security objectives from being achieved

Asset: Anything of value or importance that is used, produced, or protected within the IP

Attack Point: An access location or means through which a threat can be realized against an asset

**Attack Surface**: A set of attack points (can be applied to multiple assets).

**Concern** (**Consequence**): The potential harm that a threat poses to an asset

**Fully Qualified Name:** In Verilog, a design element with its module name. Format: <module\_name>.<asset\_name>. In VHDL, a design element with its component name. Format: <component\_name>.<asset\_name>. Other languages may have corresponding notations.

Integrated Circuit: An electronic design (e.g. SoC, ASIC, etc.) that consists of multiple IPs

**Integrator**: The entity that integrates IP into an electronic design

IP: Intellectual Property – The RTL or other design representation that is the subject of this standard

**IP Bundle**: The collateral that is supplied by the IP Provider which contains everything an Integrator needs to incorporate the IP

**IP Provider**: The entity that supplies an IP

Mitigation: A solution that reduces the risk or consequence of an attack

RTL: Register-Transfer Level – A design abstraction that models a digital circuit

**Security Objective**: A measurable way to achieve a security goal. For example, a security goal may be "protect an asset". A security objective would be "Confidentiality" on that asset as a means of protection. This standard identifies Confidentiality, Integrity, and Availability [B3] as security objectives.

**Threat (Attack):** Anything that can potentially adversely affect an asset

Threat Model: A collection of threats that are in scope for an electronic design

Vulnerability: A weakness in the IP that could be exploited

Weakness: A way in which an IP fails to protect an asset

# 3.2 Acronyms and abbreviations

| ADC      | Analog-Digital Converter                                 |

|----------|----------------------------------------------------------|

| AES      | Advanced Encryption Standard                             |

| API      | Application Programming Interface                        |

| APIC     | Advanced Programmable Interrupt Controller               |

| APSO     | Attack Points Security Objective                         |

| ASIC     | Application Specific Integrated Circuit                  |

| BIST     | Built-In Self-Test                                       |

| CDMA/GSM | Code Division Multiple Access / Global System for Mobile |

| CIA      | Confidentiality, Integrity, Availability                 |

| CISC     | Complex Instruction Set Computer                         |

| CPU      | Central Processing Unit                                  |

| CWE      | Common Weakness Enumeration                              |

| DAC       | Digital-Analog Converter                                   |

|-----------|------------------------------------------------------------|

| DDR       | Double Data Rate                                           |

| DRAM/SRAM | Dynamic Random-Access Memory / Static Random-Access Memory |

| DSP       | Digital Signal Processor                                   |

| EDA       | Electronic Design Automation                               |

| EEPROM    | Electrically Erasable Programmable ROM                     |

| FPGA      | Field Programmable Gate Array                              |

| FSM       | Finite State Machine                                       |

| GPIO      | General Purpose Input/Output                               |

| GPS       | Global Positioning System                                  |

| GPU       | General Processing Unit                                    |

| HDL       | Hardware Description Language                              |

| HMAC      | Keyed-Hash Message Authentication Code                     |

| I2C       | Inter-IC bus                                               |

| IC        | Integrated Circuit                                         |

| IP        | Intellectual Property                                      |

| IPSA      | IP Security Assurance (Workgroup)                          |

| JSON      | JavaScript Object Notation                                 |

| JTAG      | Joint Test Action Group                                    |

| LSB       | Least Significant Bit                                      |

| MMC       | Memory Management Controller                               |

| MSB       | Most Significant Bit                                       |

| NoC       | Network on Chip                                            |

| NVRAM     | Non-Volatile RAM                                           |

| OTP       | One-Time Programmable                                      |

| PCIe      | Peripheral Component Interconnect Express                  |

| PHY    | Physical layer                                                   |

|--------|------------------------------------------------------------------|

| RISC   | Reduced Instruction Set Computer                                 |

| RNG    | Random Number Generator                                          |

| ROM    | Read-Only Memory                                                 |

| RSA    | Rivest, Shamir, and Adelman                                      |

| RTL    | Register-Transfer Level                                          |

| SA-EDI | Security Annotation for Electronic Design Integration            |

| SHA    | Secure Hash Algorithm                                            |

| SoC    | System on Chip                                                   |

| SWKB   | Security Weakness Knowledge Base                                 |

| TPU    | Tensor Processing Unit                                           |

| URI    | Uniform Resource Identifier                                      |

| USB    | Universal Serial Bus                                             |

| VHDL   | Very High Speed Integrated Circuit Hardware Description Language |

# 4. Background

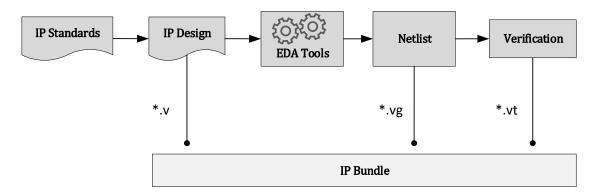

In today's IP development and delivery process, there's no standard guidance in security assurance. At the basic level, an IP is defined based on standards such as Verilog, VHDL, etc. that are compiled and synthesized using EDA tools to produce outputs such as netlists, place & route databases, etc. As it pertains to the standard in this document, the focus of discussion is the IP design (i.e. RTL), gate-level netlist, and any testbench that's produced. At a high level, the workflow is shown in Figure 1.

Figure 1, Existing IP Workflow

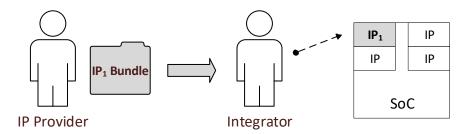

The file extensions shown are examples only to establish the context of what is contained in an IP Bundle. Additionally, the "bundle" may contain files such as documentation, executables, configuration files, etc. This bundle is what is being offered as an IP for the Integrator to incorporate into their product (e.g. SoC), as shown in Figure 2.

Figure 2, IP Delivery

The Integrator will unpack the IP Bundle to extract its contents and execute simulation tests to prove it is functionally sound. After performing initial sanity checks or functional verification, the Integrator incorporates the IP into the SoC. Once integrated, additional tests are performed to verify the IP is behaving properly with other IPs in the product. The process is repeated for each IP that is integrated into the SoC.

There is a notable gap in the IP development and delivery workflow, which does not include a statement of security concerns that an Integrator inherits or introduces when accepting an IP from a provider. This standard will provide guidance as to what IP security assurance collateral is needed and how the collateral should be consumed to close this gap.

# 5. SA-EDI Methodology

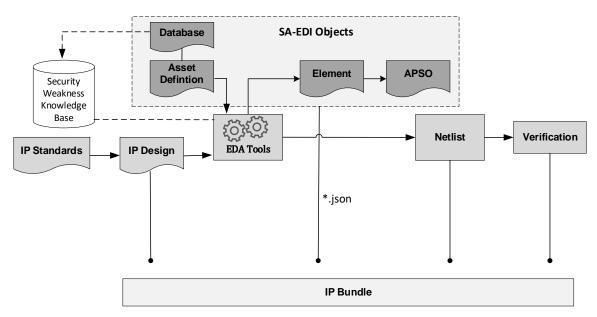

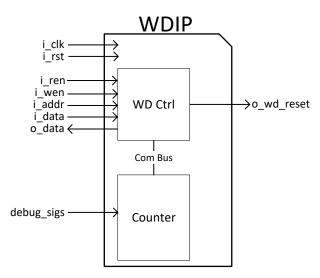

The standard introduces new collateral into the IP bundle which is shown in Figure 3. This collateral includes data objects that represent assets, database, elements, and attack points and security objectives. These objects are discussed in detail in section 7. As additions, they can be added to an existing workflow without modification to the IP design.

Figure 3, SA-EDI IP Bundle

The Asset Definition data object identifies critical or valued material within the IP. It also contains a Database data object that provides information about a Security Weakness Knowledge Base. These data objects are inputs into EDA tools that create Element data objects. The Element data objects contain ports and parameters that influence the behavior of the asset and include potential security weaknesses that are associated with the asset and/or IP type. The Element data objects are used to create Attack Points Security Objective (APSO) data objects. APSO data objects associate a security objective such as confidentiality, integrity, availability, to a list of ports or parameters thus creating an attack surface. These APSO data objects eventually build the threat model for the IP Integrator to use. The details of these objects are in later sections of this document.

The data objects in Figure 3 are shown as JSON format. This is detailed later in section 7.1.

It is also worth noting that the Element objects can be created manually without an EDA tool.

The database labeled "Security Weakness Knowledge Base" contains security weaknesses that are known due to industry experience and/or security researchers. The standard allows the use of multiple databases from multiple sources. The details of how such a knowledge base can be utilized are listed in a later section.

### 5.1 IP Bundle

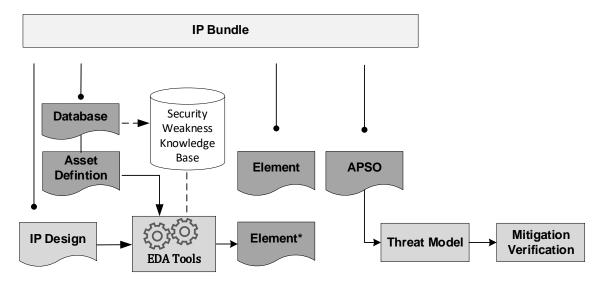

Upon receiving the IP Bundle, the Integrator will use the new data objects to create a threat model that is specific to the integrated circuit with respect to the IP. This is shown in Figure 4. The Integrator will repeat some of the steps that the IP Provider performed in order to verify that the SA-EDI data objects were indeed derived from the IP definition. Performing this verification is optional, however highly recommended by the standard.

Figure 4, SA-EDI Integrator

The Integrator, using the Asset Definition and Database in the bundle and the same Security Weakness Knowledge Base, generates an Element data object. This object is labeled "Element\*" in Figure 4 and should correspond to the same assets that were defined in the IP bundle. Once generated, the Integrator compares the contents of the Element\* object to the contents of the Element object in the bundle. This comparison can be done by visual inspection or by using a tool. If the contents are the same, then the Integrator knows the security assurance collateral corresponds to the RTL and can proceed with integration. If the contents are not the same, then the Integrator and the IP Provider need to resolve the differences before integrating the IP into the IC. Mismatches may be caused by RTL changes after the Element object was generated or that there was an error in the generation of the Element object itself.

The Integrator then reviews the Attack Point Security Objective (APSO) data objects in the bundle to determine which ones are in scope for the IC. This will become the threat model which contains mitigations to be verified. The Integrator may also create additional APSO objects that are product specific for this IP. These additions become part of the IC's threat model for verification.

# 6. Security Weakness Knowledge Base

The Security Weakness Knowledge Base (SWKB) is a database or repository that contains security concerns that are associated with hardware IP and its integration. The term SWKB is generic and does not represent a specific database. It is instead used to reference existing databases such as the Common Weakness Enumeration (CWE) [B2] or even a proprietary database. The standard allows for the use of multiple databases in multiple locations. Additionally, the SWKB should support an API that allows for software queries in order to aid in automation.

The standard requires that a SWKB support searchability on IP and asset categories or types. This requirement makes it possible for security weaknesses to be associated with a specific IP or asset. The IP family types are listed in Table 1. Along with the types are definitions and examples to help provide more clarification about the IP family. This table has the capability to support additional IP family types, which can then be shared with Integrators to preserve the associations and methodology workflow.

The family types defined in Table 1 are intended to be high-level, generic classifications. They should not be used as detailed descriptions of the IP itself. Therefore, an IP may be classified by several family types and the standard does not prohibit assigning multiple family types to a single IP.

**Table 1, IP Family Types**

| 1 Accelerator IP dedicated to offload a specific workload to enperformance 2 Analog & Mixed- Signal IP that controls or senses the electricals for communication, which receives or transmits sign conditioned outside of a system's digital domain IP designed to manipulate audio/video data | mathematical, compression PHY, ADC, DAC  nals Coders/Decoders, speech recognition, format converters |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| 2 Analog & Mixed-<br>Signal IP that controls or senses the electricals for<br>communication, which receives or transmits sig<br>conditioned outside of a system's digital domain                                                                                                               | PHY, ADC, DAC  gnals  n  Coders/Decoders, speech recognition, format converters                      |

| Signal communication, which receives or transmits sig conditioned outside of a system's digital domain                                                                                                                                                                                         | coders/Decoders, speech recognition, format converters                                               |

| conditioned outside of a system's digital domain                                                                                                                                                                                                                                               | Coders/Decoders, speech recognition, format converters                                               |

|                                                                                                                                                                                                                                                                                                | Coders/Decoders, speech recognition, format converters                                               |

| 3 Audio/Video IP designed to manipulate audio/video data                                                                                                                                                                                                                                       | recognition, format converters                                                                       |

| if designed to mainparate addition video data                                                                                                                                                                                                                                                  |                                                                                                      |

|                                                                                                                                                                                                                                                                                                |                                                                                                      |

| 4 Bus/Interface IP implementing an interconnect among elemen                                                                                                                                                                                                                                   |                                                                                                      |

| and/or within a computing system                                                                                                                                                                                                                                                               | GPIO, AXI                                                                                            |

| 5 Communications IP designed to transmit/receive information                                                                                                                                                                                                                                   | Modulator/Demodulator,                                                                               |

|                                                                                                                                                                                                                                                                                                | 802.11, Bluetooth,                                                                                   |

|                                                                                                                                                                                                                                                                                                | CDMA/GSM                                                                                             |

| 6 Controllers A circuit hard-wired (e.g. Finite State Machine)                                                                                                                                                                                                                                 |                                                                                                      |

| react in a closed-loop control system or other lin                                                                                                                                                                                                                                             | mited Memory, Storage                                                                                |

| context, to control another entity                                                                                                                                                                                                                                                             |                                                                                                      |

| 7 Counter/Timer IP reflecting the passage of time in oscillations                                                                                                                                                                                                                              | or Real Time Clock, Watchdog,                                                                        |

| human units                                                                                                                                                                                                                                                                                    | Monotonic Counter                                                                                    |

| 8 Memories Volatile (transient) data storage                                                                                                                                                                                                                                                   | DRAM, SRAM                                                                                           |

| 9 Microcontroller A specialized processor acting as a programmab                                                                                                                                                                                                                               | ble 8051, Nios                                                                                       |

| controller                                                                                                                                                                                                                                                                                     |                                                                                                      |

| 10 Power Management IP which controls and/or monitors the power sta                                                                                                                                                                                                                            |                                                                                                      |

| system                                                                                                                                                                                                                                                                                         | controllers or monitors                                                                              |

| 11 Processors A programmable computing engine                                                                                                                                                                                                                                                  | CPU, GPU, TPU                                                                                        |

| 12 Security IP designed to protect assets                                                                                                                                                                                                                                                      | Cryptography, authorization,                                                                         |

|                                                                                                                                                                                                                                                                                                | tamper detection, access                                                                             |

|                                                                                                                                                                                                                                                                                                | controls, RNG                                                                                        |

| 13 Storage non-volatile (permanent) data storage                                                                                                                                                                                                                                               | EEPROM, eFuse, flash, ROM,                                                                           |

|                                                                                                                                                                                                                                                                                                | OTP, NVRAM                                                                                           |

| 14 Test/Debug IP designed to verify functionality and identify:                                                                                                                                                                                                                                | root JTAG, BIST, boundary scan,                                                                      |

| cause of defects                                                                                                                                                                                                                                                                               | pattern generator                                                                                    |

| 15 Transducers IP which converts energy from one form to another                                                                                                                                                                                                                               | ther, sensors, actuators                                                                             |

| such as physical to electrical                                                                                                                                                                                                                                                                 |                                                                                                      |

| 16 <user defined=""> This type is used to accommodate families that</user>                                                                                                                                                                                                                     |                                                                                                      |

| not been defined in this table (e.g. proprietary II                                                                                                                                                                                                                                            |                                                                                                      |

| add a family, the value should have the prefix "                                                                                                                                                                                                                                               | UD:".                                                                                                |

Table 2 shows the classification types for assets. These types provide more information about the asset (e.g., what makes it an asset) and can be used to associate additional security weaknesses to the IP itself. Similar to the IP family types, the asset types are intended to be high-level, generic classifications in which several may be used to describe a single asset.

### Table 2, Asset Type

| # | Name                     | Definition                                                                                                                                                                | Examples                                             |

|---|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 1 | Critical                 | Material that is critical for proper functionality. Without this asset, the IP would not be able to function.                                                             | Timers/Counters, clock generators                    |

| 2 | Secret                   | Material that requires confidentiality and should not be accessible outside the IP                                                                                        | Password, cryptographic keys                         |

| 3 | Sensitive                | Material that requires integrity but not necessarily confidentiality.                                                                                                     | Root of Trust (e.g. Asymmetric public key), fuse/OTP |

| 4 | Control                  | Material used to alter and/or control the state of the IP. This material can also setup or configure the IP.                                                              | FSM, control register                                |

| 5 | Cryptographic            | Material that is part of a cryptographic operation                                                                                                                        | AES, RSA, SHA, HMAC, RNG                             |

| 6 | Code/Data                | Material that contains information which can alter the behavior of the IP                                                                                                 | Storage (Volatile/Non-volatile)                      |

| 7 | Compute                  | Material that is part of an execution engine that operates on opcodes or instructions                                                                                     | CISC, RISC, CPU, GPU                                 |

| 8 | <user defined=""></user> | This type is used to accommodate asset types that have not been defined in this table (e.g. proprietary IP). To add an asset type, the value shall have the prefix "UD:". | UD: CustomIP                                         |

### 6.1 Format

To support the standard, a SWKB shall provide the following attributes for each entry:

- a) **Title**: A brief and high-level description about the weakness, normally a single sentence or phrase.

- b) **Reference number**: A unique identifier within the knowledge base. It will be used in the Element data object (Section 7.4) to reference a specific entry.

- c) **Description**: A detailed description of why the weakness is a problem or concern. It may include possible unwanted behaviors, affected resources, etc.

- d) **Consequence**: A classification of the risk(s) due to the weakness as confidentiality, integrity, and/or availability. The impact of the consequence should be captured as well.

- e) **Applicability**: A list of IP families (Table 1) and/or asset types (Table 2) that may be impacted by the security weakness.

- f) **Modes of Introduction**: A list of lifecycle phases in which the weakness could have been introduced. Some examples are architecture, design, implementation, integration, manufacturing or provisioning, etc.

- g) **Mitigations**: This attribute lists techniques that are intended to minimize the severity of the weakness. The attribute should include relevant lifecycle phases in which mitigations can be introduced. See reference f) above.

Table 1 and Table 2 are used alone or in combination to associate security weaknesses to an Asset Definition data object. In addition, the standard allows the use of any keywords or text in the data fields of an entry.

# 6.2 Specifications

The rules are as follows:

- a) The SWKB database should reference IP Family types as shown in Table 1, column "Name" into the appropriate entries by string value.

- b) The SWKB database should reference Asset Functionality types as shown in Table 2, column "Name" into the appropriate entries by string value.

# 7. Data Objects

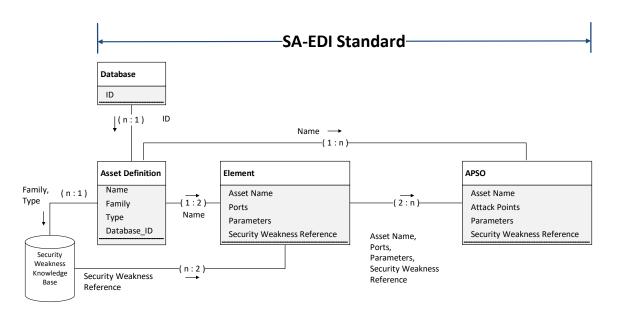

The data objects (Asset Definition, Database, Element, and Attack Points Security Objective) and SWKB are linked via attributes as shown in Figure 5. Please note that the associated attributes between the data objects are shown and not the complete list of attributes in each object. The variable n in the diagram represents one or more objects and not equivalence or a specific value. The Asset Definition object uses the attribute  $Database\_ID$  to reference a SWKB(s). This reference is linked to the attribute ID of the Database object. The Database object defines the properties of a SWKB. The Asset Definition object uses Family and Type attributes to identify entries in the SWKB that match the values in (e) in section 6.1. The Element object uses Security Weakness Reference attribute to link to those entries in the SWKB. This attribute matches the values in (b) in section 6.1. The Asset Definition and Element objects are linked by the Name attribute as defined in the Asset Definition object.

The Element object is used to create the Attack Points Security Objective (APSO) data object and the attributes Asset Name, Ports, Parameters, and Security Weakness Reference are the associations between them. The value in the Asset Name attribute matches the Name attribute of the Asset Definition object. The value(s) in the Ports attribute correlates (may not be 1:1) to the value(s) in the Attack Points attribute of the APSO object.

There may be circumstances in which an Element object is not created, however there is still a need to create an APSO object to identify a security objective to an asset. In this case, the APSO object may be created from the Asset Definition object and the attribute *Asset Name* will be associated to *Name*, respectively.

Figure 5, SA-EDI Associations

### 7.1 Data Object Language

Data objects shall be machine readable and should be human readable. The standard uses JavaScript Object Notation (JSON)[B4] as its data modeling language. JSON was chosen due to its adaptability and small footprint for easier documentation. The examples use JSON 2019-09. However, any version greater than or equal to Draft 4 can be used since required field capabilities were introduced in Draft 4, which is needed to support attributes that are required by the standard.

The JSON schema for each of the data objects are defined in section Annex A. The schema may be extended to support future attributes and/or specific use-cases. For simplicity, data objects and objects are equivalent throughout the standard.

### 7.2 Asset Definition

The Asset Definition data object is the critical dependency in the standard. All other data objects are derived from this object. Therefore, defining assets correctly is crucial to completing a proper threat model.

The Asset Definition object is used to identify assets within the IP. An asset is anything of value or importance that is critical to proper behavior which require security objective protections. An asset can be identified as a port, module, register, or another object in the design. The paper [B1] provides more information, along with examples, about how to possibly identify assets within an IP. In addition, there's a use-case example in Annex B that highlights the complete methodology.

Once an asset is identified, its definition is comprised of the attributes defined in Table 3. The attribute *Name* is used to reference the asset in RTL and shall match its corresponding text in the source. Each asset will have its own Asset Definition data object. The attributes are provided by the IP Developer and will be used later to create the Element data object.

# **Table 3, Asset Definition Data Object**

| Attribute   | Required | Type                                  | Definition                                                                                                                                                                                                      |

|-------------|----------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name        | Yes      | String (case-sensitive <sup>1</sup> ) | Full hierarchical path name of the asset as defined in the RTL source                                                                                                                                           |

| Description | No       | String                                | Brief description about the asset (e.g., what makes it an asset, its purpose, etc.). This is not a required field however it is strongly recommended since it provides useful information to the IP Integrator. |

| Family      | Yes      | Array of Strings                      | Describes the IP type or family. The values are listed in Table 1. The value may be the numeric string or string name. There may be more than one type that is applicable.                                      |

| Туре        | Yes      | Array of Strings                      | Describes the asset type. The values are listed in Table 2. The value may be the numeric string or string name. There may be more than one type that is applicable.                                             |

| Database_ID | No       | Array of Strings                      | Reference to a SWKB. The string should match the attribute value of <i>ID</i> in Table 4. This is an array to support multiple databases.                                                                       |

# 7.2.1 Specifications

The rules are as follows:

- a) An IP may have multiple assets.

- b) An Asset Definition object shall reference a single asset.

- c) If the asset is an array, it is assumed the entire array is the asset unless a specified range is included in the *Name* attribute.

- d) If an asset is in several ranges of an array, then each range shall have its own Asset Definition object.

### 7.3 Database

The Database data object is used to provide details about a security weaknesses database that is to be used in the methodology flow. A Database object is associated to an Asset Definition object via the *ID* attribute in Table 4. Since the methodology supports the use of multiple databases, there may be many Database objects associated to an Asset Definition object.

The Database object is not required if a security weaknesses database is not used.

<sup>&</sup>lt;sup>1</sup> Case-sensitivity may be dependent on the language of the RTL source.

# **Table 4, Database Data Object**

| Attribute   | Required | Туре   | Definition                                                                                                                                                                                        |

|-------------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ID          | Yes      | String | A unique identifier that is associated to a SWKB. This may be the name of the database. This attribute is referenced in the Asset Definition object in the <i>Database_ID</i> attribute (Table 3) |

| Description | No       | String | Brief description about the database (e.g. how to use it, types of weaknesses, etc.)                                                                                                              |

| URI         | Yes      | String | URI locator of the security weaknesses database                                                                                                                                                   |

| Version     | Yes      | String | Version identifier of the security weaknesses database                                                                                                                                            |

# 7.3.1 Specifications

The rules are as follows:

- a) Every SWKB version shall have at least one Database object associated with it.

- b) A Database object may be associated with one or more Asset Definition objects.

### 7.4 Element

The Element data object is created when Asset Definition object(s) are defined. An Asset Definition object provides enough information for a tool (e.g., EDA) to generate Element objects. An Element object defines the top module influencers (i.e., elements) of the IP that can affect and/or observe the behavior of the asset. These elements may include input/output ports and/or configuration parameters in the RTL. These are access points that either: 1) an adversary can use to affect the asset's behavior, or 2) an Integrator needs to take into consideration to ensure proper protections are in place.

An Element object is associated with an Asset Definition object via the Asset Identifier, which is defined in section 7.2. Every Asset Definition object shall have at least one associated Element object. Element objects are categorized by the attribute *Direction* shown in Table 5. This attribute represents the direction of influence for the *Ports* attribute. Therefore, the signals listed in *Ports* shall all be in one direction. If a port is bidirectional, it may be listed in both the "Input" and "Output" Element objects.

### **Table 5, Element Data Object**

| Attribute                         | Required | Туре                                            | Definition                                                                                                                                                         |

|-----------------------------------|----------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Asset Name                        | Yes      | String                                          | Reference to the attribute <i>Name</i> as defined in Table 3                                                                                                       |

| Direction                         | Yes      | Enumeration                                     | Defines the direction of the <i>Ports</i> attribute:  1. Input 2. Output                                                                                           |

| Security<br>Weakness<br>Reference | No       | Array of Strings                                | Security weakness reference(s) from the SWKB. The format is dependent on the format of the entries in the database.                                                |

| Ports                             | Yes      | Array of Strings (case-sensitive <sup>2</sup> ) | Ports exposed at the integration level that influence or observe the behavior of an asset                                                                          |

| Parameters                        | No       | Array of Strings (case-sensitive <sup>2</sup> ) | Configuration parameters in the RTL that are associated with the asset. Since parameters are language dependent, the text should match the syntax of the language. |

# 7.4.1 Specifications

The rules are as follows:

- a) An Element object shall reference only one Asset Definition object.

- b) No more than one "Input" Element object shall reference the same Asset Definition object.

- c) No more than one "Output" Element object shall reference the same Asset Definition object.

- d) The *Asset Name* attribute must match the text, including case, in the attribute *Name* in the Asset Definition object.

- e) If multiple Database objects are defined in the Asset Definition object then each entry in the attribute *Security Weakness Reference* shall include the value of *ID* in Table 4.

# 7.5 Attack Points Security Objective (APSO)

The Attack Points Security Objective (APSO) data object is the starting point for the Integrator to understand the inherited security concerns and objectives. The intent of the APSO object is to assign a security objective to an attack surface of an asset and any conditions that may violate that objective. It may be derived directly from Element objects or an Asset Definition object if there are side-channel concerns to address. The supported security objectives are Confidentiality, Integrity, and Availability which are aligned with the definitions in the NIST SP 800-100 handbook[B3]. The APSO object may include applicable security weakness references identified in the Element object(s).

An APSO object may be created without an association to an Element object. An asset may lack a fan-in and/or fan-out that reaches the IP boundary. In this case, there will be no need for an Element object, but there may be security objectives pertaining to the asset, for which an APSO object is required.

An example could be the entropy source of a random number generator (RNG) integrated in the IP. This entropy source might not be exposed to the integration layer via a port, so there will be no Element object associated to the Asset Definition object. However, the asset may still require a security objective (e.g., Integrity), therefore an APSO object may be created with the *Attack Points* attribute empty. These types of

<sup>&</sup>lt;sup>2</sup> Case-sensitivity may be dependent on the language of the RTL source.

APSO objects are used to identify implicit security concerns such as side-channel or injection attack points associated with a particular asset.

An IP Provider may create APSO objects that address security objectives external to the IP. These objects are intended to provide additional integration guidance. For example, an asset's port may have requirements to support a security objective, such as Availability. In this case, the *Description* attribute could recommend that "this port should be directly connected to the IC's reset logic and not gated by any logic". This object provides additional guidance on how the IP should be integrated.

# Table 6, APSO Data Object

| Attribute                            | Required | Туре             | Definition                                                                                                                                                                                                                                                                                                              |

|--------------------------------------|----------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                 | Yes      | String           | Unique identifier for the security objective that is associated with this <i>Asset Name</i> . The <i>Name</i> need not be unique across multiple assets.                                                                                                                                                                |

| Asset Name                           | Yes      | String           | Reference to the <i>Name</i> attribute in Table 3                                                                                                                                                                                                                                                                       |

| Security<br>Objective                | Yes      | Enumeration      | Describes the security objective required for the asset. There should only be one security objective identified per APSO object.  1. Confidentiality 2. Integrity 3. Availability                                                                                                                                       |

| Description                          | No       | String           | Additional information about the security objective                                                                                                                                                                                                                                                                     |

| Condition                            | No       | SVA expression   | Condition under which the security objective is violated, expressed in SystemVerilog Assertion (SVA) syntax. An example may be a lock bit, which protects the integrity of a register, not being enabled. All RTL signals used in the expression should be qualified such that it can be evaluated at the IP top level. |

| Security<br>Weakness<br>Reference    | No       | Array of Strings | Reference to Security Weaknesses Reference attribute identified in Table 5.                                                                                                                                                                                                                                             |

| Additional<br>Security<br>Weaknesses | No       | Array of Strings | Additional weaknesses that were not identified in attribute <i>Security Weakness Reference</i> . These can be newly discovered or use-case/customer specific weaknesses.                                                                                                                                                |

| Attack Points                        | No       | Array of Strings | Ports listed in Table 5 that are associated with this security objective                                                                                                                                                                                                                                                |

| Parameters                           | No       | Array of Strings | Configuration parameters listed in Table 5 that are associated with this security objective                                                                                                                                                                                                                             |

# 7.5.1 Specifications

The rules are as follows:

- a) The combination of Name and Asset Name shall be unique.

- b) An APSO object shall have exactly one Security Objective defined.

- c) An APSO object shall apply to exactly one Asset Definition object.

- d) An APSO object may have no associated Element objects, in which case the attribute *Attack Points* shall be empty.

### 8. Threat Model

The next step in the methodology is the creation of a threat model for the IC. This is performed by the Integrator and may be created from applicable APSO objects. The APSO objects may come from both the IP Provider and the Integrator.

APSO objects are based on the architecture and design of the IP as a standalone component. Additionally, the IP Provider may have created APSO objects based on potential use-cases of the IP in an integrated circuit such as an SoC. When the Integrator examines the APSO objects, some may not be relevant to the IC. For example, there may be an APSO object that addresses confidentiality concerns on the counter of a watchdog timer, the counter being the asset. The concern is that by leaking the count value, an attacker could gain an advantage (e.g. the length of time remaining to launch an exploit). This may not be relevant to the security of the IC. If the watchdog is being used for boot ROM execution and gets disabled when this execution is finished, confidentiality is probably not an objective due to the limited agents that are out of reset at the time. Therefore, this APSO object would not apply to the use-case of the IC.

Once the Integrator has evaluated which IP level APSO objects are in scope for the IC, the next step is to identify which IC level APSO objects are relevant to the integration of the IP. Using the watchdog example, the Integrator may add an APSO object that pertains to the availability of the watchdog's reset assertion due to a timeout. The object would have the security objective Availability to ensure that there is no gating logic on the watchdog reset.

When the IC level APSO objects have been created, the integration Threat Model is complete for the IP. The standard does not define the format of a threat model beyond the APSO data object definition. This allows the flexibility of converting APSO objects into other formats that align with an industry or company-specific verification process.

# 9. Workflow Compliance

The intent of this section is to state the responsibilities of both the IP Provider and Integrator in the workflow. A compliant IP Bundle includes the applicable Asset Definition, Database, Element, and APSO data objects. See section 7.5 for cases where an Element object is not required. See section 7.3 for cases where a Database object is not required. Table 7 shows the steps of the workflow. Steps #1-5 can be followed by an IP Provider to create a compliant IP Bundle. Steps #6-11 can be followed by an Integrator to integrate and verify a compliant IP Bundle.

# Table 7, Workflow

| Step# | Owner       | Details                                                                         | Output               |

|-------|-------------|---------------------------------------------------------------------------------|----------------------|

| 1     | IP Provider | Identify a database of known weaknesses and create a Database object(s)         | Table 4,             |

|       |             |                                                                                 | Database Data        |

|       |             |                                                                                 | Object               |

| 2     | IP Provider | Identify asset(s) in the IP and create an Asset Definition object(s) for each   | Table 3, Asset       |

|       |             | asset                                                                           | Definition Data      |

|       |             |                                                                                 | Object               |

| 3     | IP Provider | Using the output of step #1 and #2, generate the Element object(s) using an     | Table 5,             |

|       |             | EDA tool. This step may also be done manually.                                  | Element Data         |

|       |             |                                                                                 | Object               |

| 4     | IP Provider | Using the output of step #3, create Attack Points Security Objective object(s)  | Table 6, APSO        |

|       |             |                                                                                 | Data Object          |

| 5     | IP Provider | Bundle all the data objects created in steps #1-4 in the IP delivery package    | IP Bundle            |

| 6     | Integrator  | Using the output of step #5, repeat step #3 to regenerate the Element object(s) | Table 5,             |

|       |             | in a file for comparison. This requires that the Integrator has access to the   | Element Data         |

|       |             | RTL source. If the Integrator is using an EDA tool, it should be functionally   | Object               |

|       |             | equivalent to the tool used in step #3. The output of this step will be used to |                      |

|       |             | verify the accuracy of the Element objects with respect to the RTL source.      |                      |

| 7     | Integrator  | Using the output of steps #5-6, the Integrator compares the locally generated   | SUCCESS or           |

|       |             | Element objects to those from the IP Bundle. This compare can be done by        | FAILURE <sup>3</sup> |

|       |             | visual inspection or by a tool. If the contents of objects are the same, then   |                      |

|       |             | report SUCCESS. This means the Element objects are consistent with those        |                      |

|       |             | in the IP Bundle. Otherwise, report FAILURE and stop the workflow.              |                      |

| 8     | Integrator  | Using the output of step #5, determine which APSO objects are in scope for      | Threat Model         |

|       |             | the IC.                                                                         |                      |

| 9     | Integrator  | Using the output of step #5, create any additional APSO objects from the        | Table 6, APSO        |

|       |             | Element objects that have security objectives at the IC level as it pertains to | Data Object          |

|       |             | the IP. Additional security weaknesses may be identified also.                  |                      |

| 10    | Integrator  | If there are any APSO objects created in step #9, add them to the IC threat     | Threat Model         |

|       |             | model                                                                           |                      |

| 11    | Integrator  | Using the output of step #10, verify the security objectives are met and the    | Verification         |

|       |             | security weaknesses are properly addressed during integration of the IP into    |                      |

|       |             | the IC.                                                                         |                      |

<sup>&</sup>lt;sup>3</sup> If FAILURE, the Integrator can either choose an equivalent IP from a different supplier or have a discussion with the IP Provider to address the discrepancies.

# Annex A: Data Object JSON Schema

This section contains JSON schemas for the data objects defined in this standard, validated against the referenced JSON schema standard.

# A.1 Asset Definition

```

{

"$schema": "http://json-schema.org/draft/2019-09/schema",

"title": "Asset Definition",

"description": "An asset is something that's critical for proper IP operation",

"type": "object",

"properties": {

"Name" : { "type" : "string" },

"Description" : { "type" : "string" },

"Family" : { "type" : "array", "items" : {"type" : "string"} },

"Type" : { "type" : "array", "items" : {"type" : "string"} },

"Database_ID" : { "type" : "array", "items" : {"type" : "string"} },

"required" : ["Name", "Family", "Type"]

}

```

### A.2 Database

```

"$schema": "http://json-schema.org/draft/2019-09/schema",

"title": "Database",

"description": "Information that defines a security weaknesses database",

"type": "object",

"properties": {

"ID" : { "type" : "string" },

"Description" : { "type" : "string" },

"URI" : { "type" : "string" },

"Version" : { "type": "string" }

},

"required" : ["ID", "URI", "Version"]

```

### A.3 Element

```

"$schema": "http://json-schema.org/draft/2019-09/schema",

"title": "Element",

"description": "An element is a relationship to the asset, directly or indirectly",

"type": "object",

"properties": {

"Asset Name" : { "type" : "string" },

"Direction" : { "type" : "string", "enum": ["Input", "Output", "None"] },

"Security Weakness Reference" : { "type" : "array", "items" : { "type" : "string"} },

"Ports" : { "type" : "array", "items" : { "type" : "string"} },

"Parameters" : { "type" : "array", "items" : { "type" : "string"} }

},

"required" : ["Asset Name", "Direction", "Ports"]

```

# A.4 Attack Points Security Objective

```

{

"$schema": "http://json-schema.org/draft/2019-09/schema",

"title": "Attack Points Security Objective",

"description": "Attack points with associated security objective",

"type": "object",

```

# A.5 SA-EDI Data Object

The SA-EDI data object may be used to collect the standard's data objects into a single JSON file. This is optional, however if provided in the IP Bundle this schema shall be used.

```

"$schema": "http://json-schema.org/draft/2019-09/schema",

"definitions" : {

"ASSET" : {

"title": "Asset Definition",

"description": "An asset is something of importance",

"type": "object",

"properties": {

"Name" : { "type" : "string" },

"Description" : { "type" : "string" },

"Family" : { "type" : "array", "items" : {"type" : "string"} },

"Type" : { "type" : "array", "items" : {"type" : "string"} },

"Database_ID" : { "type" : "array", "items" : {"type" : "string"} }

"required" : ["Name", "Family", "Type"]

},

"DATABASE" : {

"title": "Database",

"description": "Information that defines a security weaknesses database",

"type": "object",

"properties": {

"ID" : { "type" : "string" },

"Description" : { "type" : "string" },

"URI" : { "type" : "string" },

"Version" : { "type": "string" }

"required" : ["ID", "URI", "Version"]

"ELEMENT" : {

"title": "Element",

"description": "An element is a relationship to the asset",

"type": "object",

"properties": {

"Asset Name" : { "type" : "string" },

"Direction" : { "type" : "string", "enum": ["Input", "Output", "None"] },

"Security Weakness Reference" : { "type" : "array", "items" : {"type" :

"string"} },

"Ports" : { "type" : "array", "items" : {"type" : "string"} },

"Parameters" : { "type" : "array", "items" : {"type" : "string"} }

"required" : ["Asset Name", "Direction", "Ports"]

"APSO" : {

```

```

"title": "Attack Points Security Objective",

"description": "Attack points with associated security objective",

"type": "object",

"properties": {

"Name" : { "type" : "string" },

"Asset Name" : { "type" : "string" },

"Security Objective": { "type": "string",

"enum": [

"Confidentiality",

"Integrity",

"Availability"

] },

"Description" : { "type" : "string" },

"Condition": { "type": "string" },

"Security Weakness Reference": {"type": "array", "items": {"type":

"string"} },