DVCon United States Highlights

By Gabe Moretti

March 25, 2015

The first "DVCon United States" was a success. It was the 27th Conference of the series and the first one with this name to separate it from the newer DVCon Europe and DVCon India, which following their successful first events last year, will be held again this year.

Overall attendance, including exhibit-only and technical conference attendees, was 932. If we count, as DAC does, exhibitors personnel then the total number of attendees is 1213. The conference attracted 36 exhibitors, including 10 exhibiting for the first time and 6 of them headquartered outside of the US. The technical presentations were very well attended, almost always with standing room only, thus averaging around 175 attendees per session. One cannot fit more in the conference rooms than the DoubleTree has space for. The other thing I observed was that there was almost no attendee traffic during the presentations. People took a seat and stayed for the entire presentation. Almost no one came in, listened for a few minutes and then left. In my experience this is not typical and points out that the goal of DVCon, to present topics of contemporary importance, was met.

A Little History

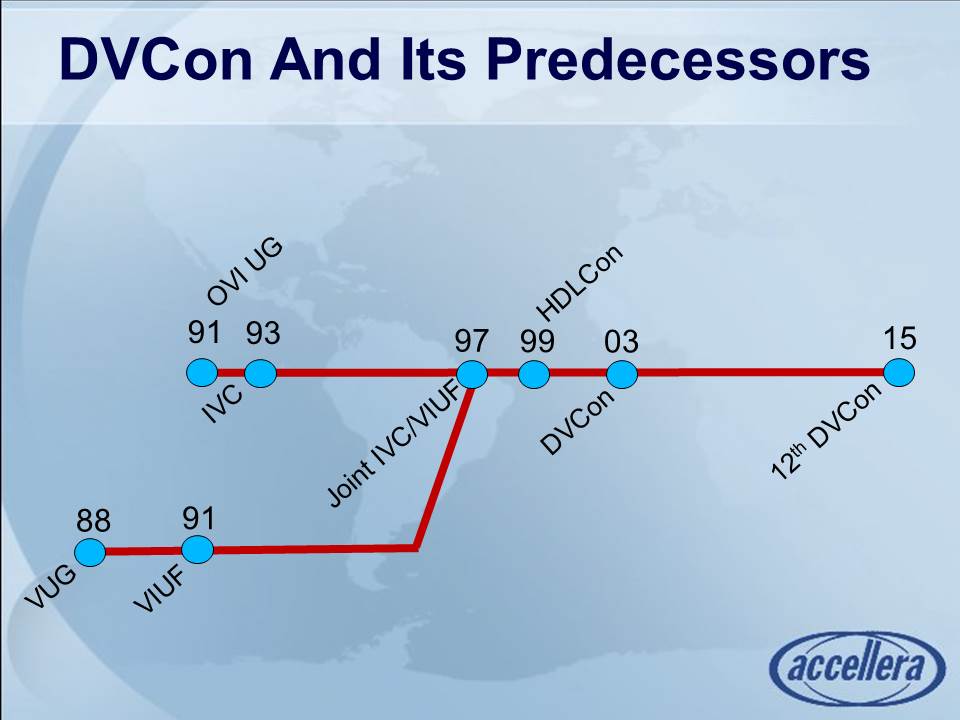

The first conference to solely address the topics of Design and Verification took place in 1988. It was organized by the VHDL Users Group (VUG) an ancestor of Accellera by two generations. The conference dealt with topics related to VHDL, the new IEEE Standard for Hardware Description Languages (HDL). In 1991 two events took place. The sponsorship of the existing conference was taken over by the VHDL International Users Forum (VIUF) and following Cadence's decision to put Verilog in the public domain, the Open Verilog International Users Group (OVI UG) held a mirror conference with Verilog as its focus. The two yearly conferences were held separately until 1997 when OVI and VIUF decided to co-locate the conferences and establish an algorithm to divide the revenue. In 1999 a further joint decision renamed the conference to HDLCon recognizing that the focus was HDL based design and verification. The following year the two organizations merged and formed Accellera. In 2003 Accellera renamed the conference DVCon since by then other languages, like SystemC for example had been used as HDLs. The figure below will help in following the history.

Technical Papers and the Posters Session

It has been clear for many years that the papers selected for presentation at DVCon not only are of the highest quality, to rival those published in the various IEEE publications, but also timely.

The Award for Best Paper Presentation, as voted by conference attendees, went to Ram Narayan and Tom Symons with Oracle Labs, for their presentation titled, "I Created the Verification Gap". The authors described the contents of the papers as follows: "It is widely accepted that the productivity gap between design and verification exists and is widening. This paper explores the various factors that contribute to this Verification Gap. While touching on factors like growing design complexity that inherently cause the gap, the focus of the paper is on those factors that are self-induced and hence within our control. Experiences of individuals in the industry have been sought, digested and shared in this paper. The objective of this paper is to evoke a sense of individual responsibility in the reader through self-inquiry."

Two Honorable Mentions were also recognized: "Mining Coverage Data for Test Set Coverage Efficiency" by Monica C. Farkash and Balavinayagam Samynathan, University of Texas at Austin, and Bryan Hickerson and Michael Behm, IBM Corp. and "Lies, Damned Lies, and Coverage" by Mark Litterick, Verilab, Inc.

To accommodate worthy papers that cannot be presented in the Technical Program due to space and time constraints, the Program Committee established a Poster session a few years ago.

Best Poster Presentations were awarded for the third year. Top honors went to Jeremy Ridgeway, Avago Technologies for his poster, "Randomizing UVM Config DB Parameters". Two Honorable Mentions were also recognized: "SystemVerilog Constraint Layering via Reusable Randomization Policy Classes" by John Dickol, Samsung Austin R&D Center and "Versatile UVM Scoreboarding" by Jacob S. Andersen, Peter Jensen and Kevin K. Steffensen, SyoSil ApS.

"DVCon has become the must-attend conference in the design and verification community for networking, technical discussion and learning opportunities," stated Yatin Trivedi, DVCon General Chair. "From the exhibit floor to the panels, tutorials and poster sessions, there are plenty of opportunities for practicing engineers to learn about new products and share ideas. There is tremendous interest in the content presented at DVCon, so Accellera has expanded DVCon to serve the global community. We look forward to our conferences in Europe and India later in the year."

"The technical program this year was remarkable," commented Ambar Sarkar, Ph.D., DVCon Program Chair. "Attendees have come to expect a high quality selection of papers and posters, and we were able to deliver just that. We consistently receive more submissions than we can accept, so we pick the best of the best for our attendees."

Process Technology and Software Growth

The keynote address this year was delivered by Aart de Geus, chairman and co-CEO of Synopsys. His speeches are always both unique and quite interesting. This year he chose as a topic "Shift Left". As one could have expected Aart's major points had to do with process technology, something he is extremely knowledgeable about. He thinks that Moore's law as an instrument to predict semiconductor process advances has about ten years of usable life. After that the industry will have to find another tool, assuming one will be required, I would add. Since, as Aart correctly points out, we are still using a 193 nm crayon to implement 10 nm features, clearly progress is significantly impaired. Personally I do not understand the reason for continuing to use ultraviolet light in lithography, aside for the huge costs of moving to x-ray lithography. The industry has resisted the move for so long that I think even x-ray has a short life span which at this point would not justify the investment. So, before the ten years are up, we might see some very unusual and creative approaches to building features on some new material. After all, whatever we will use will have to understand atoms and their structure.

A very interesting point made during the presentation is that the length of development schedules has not changed in the last ten years, content has. Development of proprietary hardware has gotten shorter, thanks to improved EDA tools, but IP integration and software integration and co-verification has used up all the time savings in the schedule.

What Dr. de Geus’s slides show is that software is and will grow at about ten times the rate of hardware. Synopsys, as are other companies, is now in the software business in a big way. Virtual prototyping and software co-verification are market segments Synopsys is very active in, and making a nice profit I may add. So, it is either a matter of definition or new market availability, but EDA companies are in the software business.

Conclusion

I think that both the keynote speech and the two panels provided enough understanding as well as thought material to amply justify attending the conference. Too often I have heard that DVCon is a verification conference: it is not just for verification as both the keynote and the panels prove. It is for all those who care about development and verification, in short for those who know that a well developed product is easier to verify, manufacture and maintain than otherwise.

DVCon India, hosted by Accellera System Initiative, will be held on September 10 and 11 in Bangalore. DVCon Europe will be held November 11-12 in Munich Germany. Both conferences will follow the format of the successful DVCon United States. So whether in India, in Europe or in the US, see you at the next DVCon.